近日英特尔在ISSCC 2025上,公布了其在半导体制造限制的一些施展,先容了备受期待的Intel 18A工艺时间,其中强调了SRAM密度的首要矫正。比年来SRAM单位的扩张仍是变得非常清贫,遭受了SRAM单位缩减放缓的问题。台积电(TSMC)在3nm制程节点上就莫得什么矫正,与5nm制程节点基本没区别,不传奇闻到2nm制程节点似乎也会有质的转变。

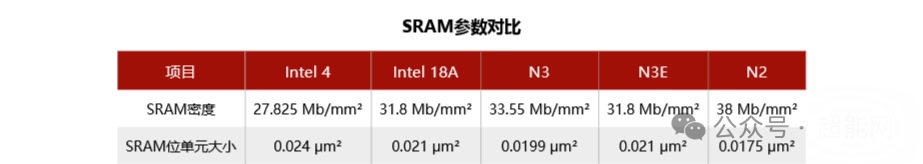

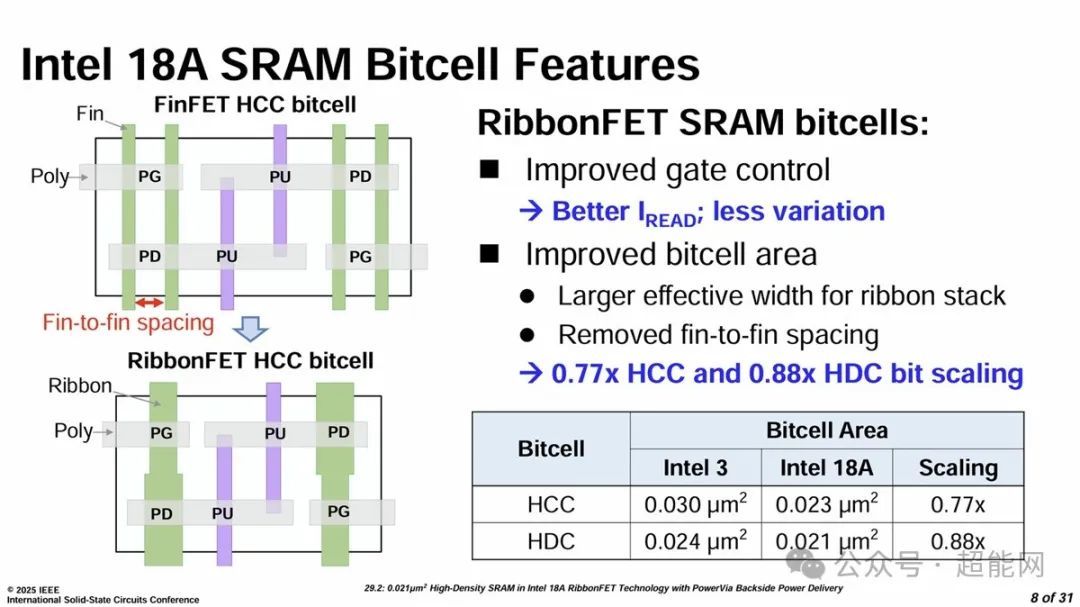

据HardwareLuxx报谈,英特尔展示了我方的恶果,称SRAM位单位尺寸将从Intel 3工艺的0.03μm²松开到Intel 18A工艺的0.023μm²,HDC也透流露同样的矫正,松开到0.021µm²,得到了可以的卓越。比拟之下,台积电N5、N3B和N2工艺的SRAM位单位大小分手为0.021µm²、0.0199μm²和0.0175μm²。

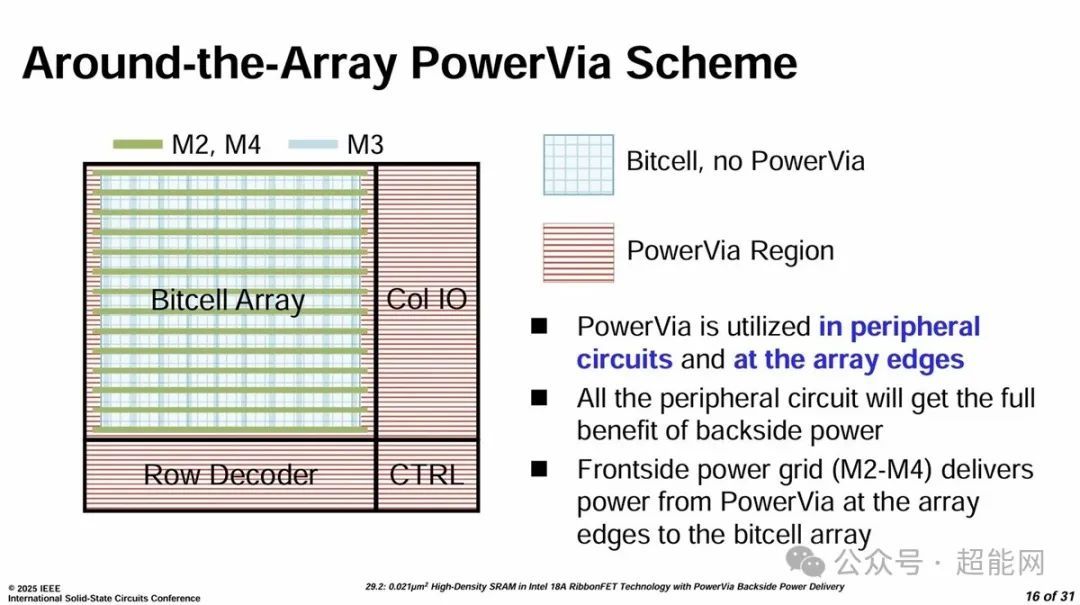

英特尔还在Intel 18A引入了PowerVia背部供电时间,这是其处治处理器逻辑区域电压下跌和搅扰的首选程序。英特尔接收了“环绕阵列”有野心,政策性地将PowerVias运用于 I/O、驱散妥协码器元件,同期优化了位单位想象,而无需正面供电。

Intel 18A的SRAM密度为31.8Mb/mm²,比起台积电N3E非常,比起N2的38Mb/mm²要忘形一些。英特尔但愿归并PowerVia和GAA晶体管架构开yun体育网,可以向台积电发起挑战,争夺像英伟达、苹果和高通这类高端客户。